CLUSTERED IC WIRING FOR CAPACITANCE BASED PHYSICAL UNCLONABLE FUNCTIONS (PUF)

Auf einen Blick

|

Forschungsprojekt |

Clustered IC wiring for Capacitance based Physical Unclonable Functions (PUF) |

|---|---|

|

Fachbereich |

Ingenieurwissenschaften |

|

Institut |

IT-/CAE-Labor |

|

Leitung |

Prof. Dr. Matthias Harter Prof. Dr. Steffen Reith |

|

Beteiligte |

Bernhard Jungk |

|

Ansprechpartner Forschungsförderung |

Dr. Michael Anton |

|

Laufzeit |

01.05.2014 – 31.01.2014 |

Projektbeschreibung

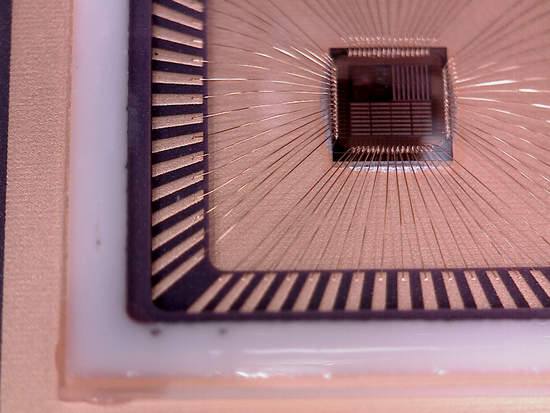

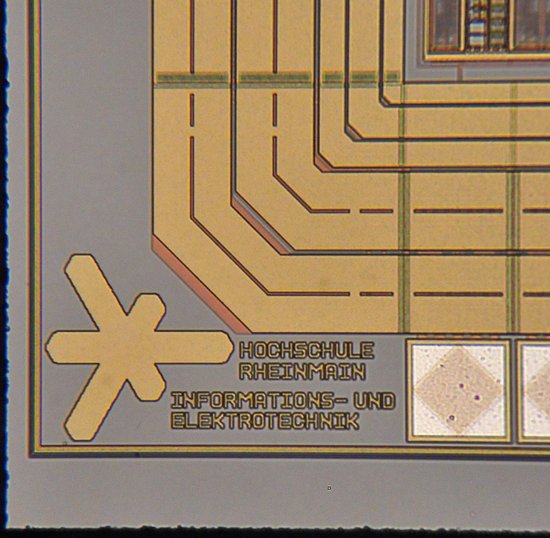

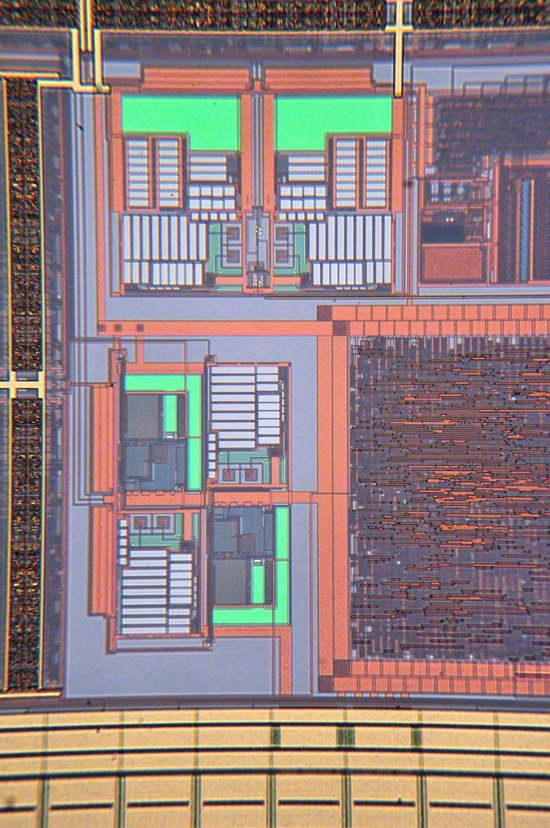

Das Projekt hat die Implementierung eines Chip-Prototypen (ASIC) zum Ziel, der den Nachweis der Praxistauglichkeit einer 2005 in Deutschland, Europa und den USA zum Patent angemeldeten Erfindung erbringen soll, die der Projektleiter im Rahmen seiner universitären Forschungstätigkeit gemacht hat. Damit soll das Projekt zur Vorbereitung und Unterstützung der Verwertungsanstrengungen (Lizenzierung der Patente) dienen, die der Projektleiter in Zusammenarbeit mit dem Technologie-Lizenz-Büro (TLB) Karlsruhe unternimmt. Konkrete Anfragen der Industrie (Halbleiterbranche) liegen beispielsweise von der Fa. Samsung vor. Mit Hilfe des Prototypen soll im Rahmen einer studentischen Arbeit ein Demonstrator (Leiterplatte und Analysesoftware) aufgebaut werden, der Messwerte von den über den Forschungsverbund Europractice zu fertigen 40 Exemplaren des Prototypen ermittelt und an einen PC zur Analyse und Ergebnisdarstellung überträgt.

Ein Aspekt der Projektes ist, dass die benötigte Entwicklungssoftware (Cadence IC Package und Europractice Membership, siehe Kostenkalkulation Sachmittel) auch für eine Lehrveranstaltung ("Chip Design und digitale Systeme") im Praktikum benutzt wird.